# On the Effects of Hot Electrons on the DC and RF Characteristics of Lattice-Matched InAlAs/InGaAs/InP HEMT's

Roberto Menozzi, *Associate Member, IEEE*, Mattia Borgarino, *Student Member, IEEE*,

Yves Baeyens, *Student Member, IEEE*, Marleen Van Hove, and Fausto Fantini, *Member, IEEE*

**Abstract**—This letter for the first time presents results of hot electron stressing of InAlAs/InGaAs/InP high electron mobility transistors (HEMT's). High drain bias, room temperature stress cycles have been applied to 0.3  $\mu\text{m}$ , SiN-passivated, lattice-matched devices, and the changes of the dc and rf (up to 50 GHz) characteristics have been studied. Both the dc and rf device gain degrade after stressing; the effect of the stress on the unity current gain cutoff frequency  $f_T$  is studied under different bias conditions. Results indicate that surface degradation may be responsible for the observed changes.

## I. INTRODUCTION

InP-BASED high electron mobility transistors (HEMT's) exhibit unparalleled performance in terms of gain and noise figure well into the millimeter-wave range, and a great deal of activity is presently being devoted to the understanding of their behavior [1], the development of ever better technologies [2], and the fabrication of both linear [3] and nonlinear [4] monolithic circuits for applications up to D-band. As a consequence of this growing interest, a few studies have been published in recent years on InP HEMT reliability, a key issue if a technology is to move out of the research labs and into the world of practical (if not commercial) applications. Researchers have so far concentrated on reliability testing using high-temperature accelerated stress [5]–[8], in one case with emphasis on the effect of the ambient gas [9]; since surface stability (together with metal contact degradation) was often identified as one of the most critical issues, different passivation techniques have been proposed for improved reliability [10]–[13].

This work for the first time reports on a different approach to the assessment of potential degradation mechanisms of InP HEMT's by focusing on the room temperature effects of hot electrons, a well-known concern due to the small channel bandgap and to the very short gates required for millimeter-wave operation. This means that if one wants to study the reliability hazards connected with hot electrons, the accelerating factor for device stress should not be the temperature, as in all of the works referenced above, but drain

bias (i.e., channel longitudinal electric field). Due to enhanced lattice scattering, high temperatures are indeed known to inhibit electron heating. Such an approach has been recently applied to GaAs-based pseudomorphic HEMT's [14]–[16], but never to InP HEMT's. We thus believe that this work represents a timely and important contribution to the topic of InP-HEMT reliability, since room temperature stressing can isolate degradation mechanisms that may get masked by others (e.g., temperature activated phenomena like metal contact degradation) at higher temperatures.

## II. EXPERIMENTS

We applied hot electron stress experiments to 0.3- $\mu\text{m}$   $\delta$ -doped  $\text{In}_{0.52}\text{Al}_{0.48}\text{As}/\text{In}_{0.53}\text{Ga}_{0.47}\text{As}/\text{InP}$  HEMT's designed and fabricated at IMEC [17], [18]. The devices, 100  $\mu\text{m}$  wide, have a typical  $F_{\min}$  of 1 dB with associated gain of 11 dB at 20 GHz. They are passivated by 200-nm-thick PECVD SiN, deposited in 25 min at 250° under growth conditions optimized for minimal stress (on 2-in. Si wafers a slightly compressive induced stress of  $1.3 \cdot 10^8 \text{ dyn/cm}^2$  was measured); the index of refraction and dielectric constant were 1.86 and 7, respectively [19]. The effect of hot electrons on the device performance was evaluated by characterizing the samples at dc and rf on wafer before and after dc accelerated stress at high  $V_{DS}$ . Device characterization was performed up to the  $V_{DS}$  allowed by device specifications (3 V), and it did not induce any sort of device degradation. The characteristics obtained before the stress match the data measured at IMEC after processing within the small dispersion among devices of the same wafer. Moreover, unstressed devices have been measured at different times over several weeks showing excellent stability. Three devices have been stressed, all of them showing the same degradation mode. The stress sequence featured four steps at  $V_{DS} = 4 \text{ V}$ ,  $V_{GS} = 0 \text{ V}$ , one at  $V_{DS} = 4.25 \text{ V}$ ,  $V_{GS} = 0 \text{ V}$ , and one at  $V_{DS} = 4.5 \text{ V}$ ,  $V_{GS} = 0 \text{ V}$ . The duration of each step was 30 min. All the experiments were done at room temperature. The presence of hot electrons and impact ionization under stress conditions is revealed by the typical bell shape of the gate current versus  $V_{GS}$  curve [16]. The observed device degradation, which is gradually enhanced by each subsequent step, is permanent, i.e., it was not recovered upon storing the devices at room temperature for a few months.

Manuscript received June 28, 1996.

R. Menozzi, M. Borgarino, and F. Fantini are with Dipartimento di Ingegneria dell'Informazione, Università di Parma, Parma 43100, Italy.

Y. Baeyens is with KULEuven, B-3001 Heverlee, Belgium.

M. Van Hove is with IMEC, B-3001 Heverlee, Belgium.

Publisher Item Identifier S 1051-8207(97)00507-2.

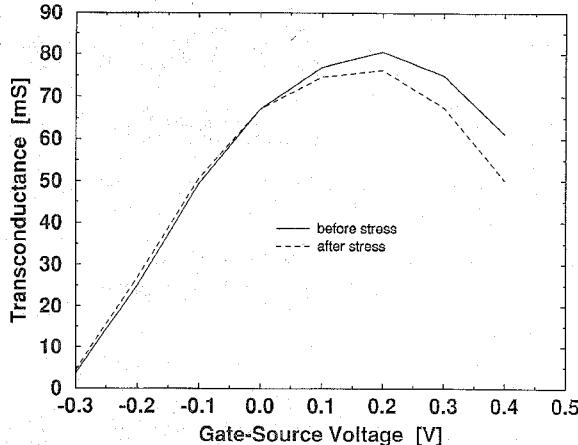

Fig. 1. Transconductance measured at  $V_{DS} = 1$  V before and after a room temperature stress sequence featuring subsequent steps at  $V_{DS} = 4, 4.25$ , and  $4.5$  V;  $V_{GS} = 0$  V during the stress, and the duration of each step is 30 min.

### III. RESULTS AND DISCUSSION

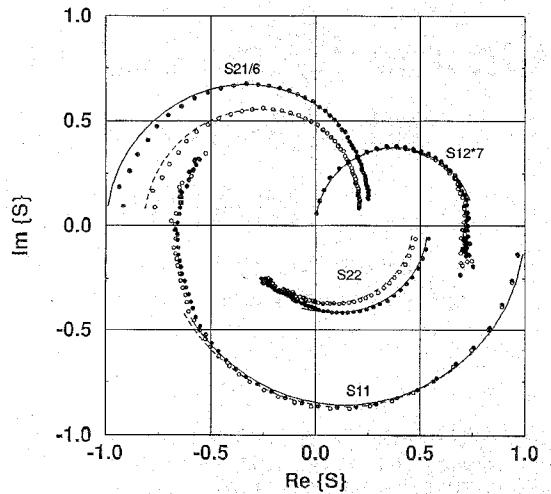

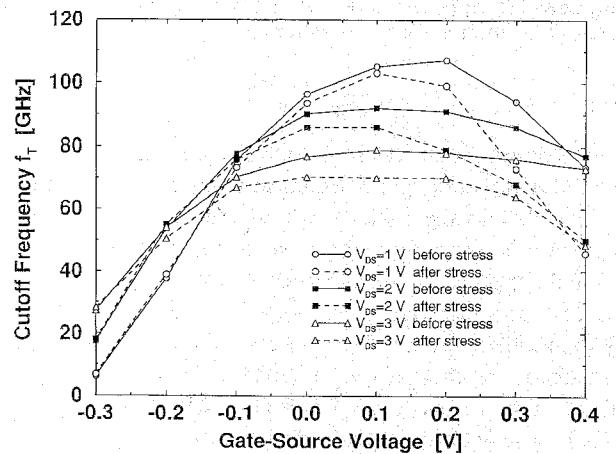

The only remarkable effect of the stress on the device dc characteristics is an  $I_{DS}$  decrease due to a transconductance compression at high  $V_{GS}$ , as illustrated by Fig. 1. The gate reverse current, due to both leakage and collection of holes generated in the channel by impact ionization, does not change significantly, indicating that the gate contact does not undergo appreciable degradation. Typical gate current values during the stress range between  $-30$  and  $50$   $\mu$ A. As to the rf behavior, we have measured the  $S$ -parameters up to 50 GHz using a HP-8510 network analyzer and a Cascade coplanar probe station. Fig. 2 shows the  $S$ -parameters of one of the devices under test, measured at  $V_{GS} = 0.3$  V,  $V_{DS} = 1$  V, both before and after the stress. The most important effect observed is a change of  $S_{21}$ , accompanied by a decrease of the magnitude of  $S_{22}$  that vanishes at high frequencies. The reduction of  $S_{21}$  reflects into a degradation of both the current gain ( $h_{21}$ ) and the power gain (MSG, MAG); consequently, both  $f_T$  and  $f_{\max}$  are degraded (at  $V_{GS} = 0.3$  V,  $V_{DS} = 1$  V,  $f_T$  decreases from 94–73 GHz,  $f_{\max}$  from 100–80 GHz). The effect of the stress on the extrinsic  $f_T$  is reported in Fig. 3. As happens with  $g_m$ , at low  $V_{GS}$  the cutoff frequency is practically unchanged by the stress; as the gate bias increases, the  $f_T$  reduction becomes more and more severe. To compare the small-signal equivalent circuit parameters extracted before and after the stress, circuit optimization was done between 1 and 25 GHz using an in-house-developed genetic algorithm [20]. Since the shape of the  $g_m$  versus  $V_{GS}$  curve allows us to rule out any significant increase of source resistance ( $R_S$ ) [6], we assumed that the device parasitics were not affected by the stress and kept them fixed at the pre-stress values. Modeled  $S$ -parameters, also reported in Fig. 2, show a very good match with measured data. The parameter values extracted at  $V_{GS} = 0.3$  V,  $V_{DS} = 1$  V indicate that the decrease of  $f_T$  is due to both a reduction of  $g_m$  ( $-16\%$ ) and an increase of  $C_{GS}$  ( $9\%$ ), while a drop of the intrinsic drain-source resistance  $R_{DS}$  ( $-15\%$ ) is responsible for the observed change of  $S_{22}$ .

From these results, and following the indications of [6], we may infer some information as to the degradation mechanism

Fig. 2.  $S$ -parameters measured at  $V_{GS} = 0.3$  V,  $V_{DS} = 1$  V before (full circles) and after (open circles) the stress of Fig. 1. The frequency ranges from 1–50 GHz. Modeled data in the 1–25 GHz range are also shown (before stress: solid lines; after stress: dashed lines).

Fig. 3. Bias dependence of the unity current gain cutoff frequency  $f_T$  before and after the stress of Fig. 1.

brought about by the hot electron stress. To begin with, significant degradation of the gate contact can be ruled out, since 1) no horizontal shift (i.e., no change of the built-in potential) appears in the  $g_m$  curve of Fig. 1 and 2) the leakage remains practically unchanged. As previously noted,  $R_S$  cannot be held responsible for the decrease of  $g_m$ , because a change of  $R_S$  would show up at every bias point, which is contradicted by Fig. 1. Moreover, at the bias points chosen for device stress, the power dissipation is such that the thermal contribution to the degradation can be considered a minor one, therefore effects related with the lattice and 2DEG quality should not be an issue. On the other hand, the increase of the degradation with gate bias is generally encountered when the device surface is affected, since carrier transport takes place close to, and is more influenced by, the surface at high  $V_{GS}$ . That the device area affected by the stress is the passivation interface is further confirmed by the observation that the deposition of the SiN layer induces a change, namely an increase, of  $g_m$  in the same  $V_{GS}$  range where the hot electron degradation develops [19]. Surface degradation may

occur due to trap creation or charge capture at the interface between the semiconductor and the passivation, a commonly observed effect of hot electrons.

#### ACKNOWLEDGMENT

The authors would like to thank G. Vannini and A. Santarelli (University of Bologna) for the use of the rf measurement equipment and M. Van Rossum (IMEC) for encouragement and helpful discussions.

#### REFERENCES

- [1] Y. Kwon, D. Pavlidis, T. L. Brock, and D. C. Streit, "Experimental and theoretical characteristics of high performance pseudomorphic double heterojunction InAlAs/In<sub>0.7</sub>Ga<sub>0.3</sub>As/InAlAs HEMT's," *IEEE Trans. Electron Devices*, vol. 42, no. 6, June 1995, pp. 1017-1025.

- [2] K. Y. Hur, R. A. McTaggart, M. P. Ventresca, R. Wohlert, L. M. Aucoin, and T. E. Krazior, "High gain AlInAs/GaInAs/InP HEMT's with individually grounded source finger vias," *IEEE Electron Device Lett.*, vol. 16, no. 9, Sept. 1995, pp. 390-392.

- [3] H. Wang, R. Lai, D. C. W. Lo, D. C. Streit, P. H. Liu, R. M. Dia, M. W. Pospieszalski, and J. Berenz, "A 140-GHz monolithic low noise amplifier," *IEEE Microwave Guided Wave Lett.*, vol. 5, no. 5, pp. 150-152, May 1995.

- [4] C. Karlsson, N. Rorsman, and H. Zirath, "A monolithically integrated F-band resistive InAlAs/InGaAs/InP HFET mixer," *IEEE Microwave Guided Wave Lett.*, vol. 5, no. 11, Nov. 1995, pp. 394-395.

- [5] M. Tutt, G. I. Ng, D. Pavlidis, and J. Mansfield, "Reliability issues of InAsAs/InGaAs High-electron-mobility transistors," in *Proc. 3rd Int. Conf. on Indium Phosphide and Related Materials*, Cardiff, U.K., 1991, pp. 349-352.

- [6] D. J. LaCombe, W. W. Hu, and F. R. Bardsley, "Reliability of 0.1  $\mu$ m InP HEMTs," in *Proc. Int. Reliability Physics Symp.*, Atlanta, GA, 1993, pp. 364-371.

- [7] H. Sasaki, K. Yajima, N. Yoshida, O. Ishihara, and S. Mitsui, "Reliability of AlInAs/InGaAs/InP HEMT with WSi ohmic contacts," in *Proc. 7th Int. Conf. on Indium Phosphide and Related Materials*, Sapporo, Japan, 1995, pp. 745-748.

- [8] Y. Ashizawa, C. Nozaki, T. Noda, A. Sasaki, and S. Fujita, "Surface related degradation of InP-based HEMT's during thermal stress," *Solid-State Electron.*, vol. 38, no. 9, pp. 1627-1630, Sept. 1995.

- [9] P. C. Chao, M. Y. Kao, K. Nordheden, and A. W. Swanson, "HEMT degradation in hydrogen gas," *IEEE Electron Device Lett.*, vol. 15, no. 5, pp. 151-153, May 1995.

- [10] K. C. Hwang, P. Ho, P. C. Chao, and K. H. G. Duh, "A novel low-temperature passivation of InAlAs/InGaAs HEMT devices by MBE," in *Proc. 4th Int. Conf. on Indium Phosphide and Related Materials*, Newport, RI, 1992, pp. 60-62.

- [11] S. Fujita, T. Noda, C. Nozaki, and Y. Ashizawa, "InGaAs/InAlAs/HEMT with a strained InGaP Schottky contact layer," *IEEE Electron Device Lett.*, vol. 14, no. 5, pp. 259-261, May 1993.

- [12] C.-S. Wu, Y.-J. Chan, J.-L. Shien, and J.-I. Chyi, "In<sub>0.52</sub>(Al<sub>0.9</sub>Ga<sub>0.1</sub>)<sub>0.48</sub>As/In<sub>0.53</sub>Ga<sub>0.47</sub>As HEMT with improved device reliability," *Electron. Lett.*, vol. 31, no. 13, pp. 1105-1106, June 22, 1995.

- [13] K. Weigel, M. Wirth, K. Hirche, and K. Heime, "Degradation effects and stabilization of InAlAs/InGaAs-HFETs," in *Proc. 8th Int. Conf. on Indium Phosphide and Related Materials*, Schwäbisch Gmünd, Germany, 1996, pp. 662-665.

- [14] C. Canali, P. Cova, E. De Bortoli, F. Fantini, G. Meneghesso, R. Menozzi, and E. Zanoni, "Enhancement and degradation of drain current in pseudomorphic AlGaAs/InGaAs HEMT's induced by hot-electrons," in *Proc. Int. Reliability Physics Symp.*, Las Vegas, NV, 1995, pp. 205-211.

- [15] Y. A. Tkachenko, C. J. Wei, J. C. M. Hwang, T. D. Harris, R. D. Grober, D. M. Hwang, L. Aucoin, and S. Shanfield, "Hot-electron induced degradation of pseudomorphic high-electron mobility transistors," in *Proc. Microwave and Millimeter-Wave Monolithic Circuits Symp.*, Orlando, FL, 1995, pp. 115-118.

- [16] R. Menozzi, P. Cova, C. Canali, and F. Fantini, "Breakdown walkout in pseudomorphic HEMT's," *IEEE Trans. Electron Devices*, vol. 43, no. 4, pp. 543-546, Apr. 1996.

- [17] Y. Baeyens, T. Skrabka, M. Van Hove, W. De Raedt, B. Nauwelaers, and M. Van Rossum, "Performance of 0.2  $\mu$ m planar doped pseudomorphic and lattice matched HEMT's on GaAs and InP," in *Proc. 23rd European Solid State Device Research Conf. (ESSDERC'93)*, Grenoble, France, 1993, pp. 753-756.

- [18] M. Van Hove, T. Skrabka, H. Bender, W. De Raedt, M. Van Rossum, and Y. Baeyens, "Optimization of ohmic contacts on lattice-matched and pseudomorphic AlInAs/InGaAs/InP," in *Mat. Res. Soc. Symp. Proc.*, vol. 326, 1994, pp. 463-468.

- [19] Y. Baeyens, M. Van Hove, W. De Raedt, D. Schreurs, B. Nauwelaers, and M. Van Rossum, "Influence of nitride passivation on the performance of InAlAs/InGaAs HEMTs," in *Proc. 24th European Solid State Device Research Conf. (ESSDERC'94)*, Edinburgh, U.K., 1994, pp. 803-806.

- [20] R. Menozzi, A. Piazza, and F. Contini, "Small-signal modeling for microwave FET linear circuits based on a genetic algorithm," *IEEE Trans. Circuits Syst. I*, vol. 43, no. 10, pp. 839-847, Oct. 1996.